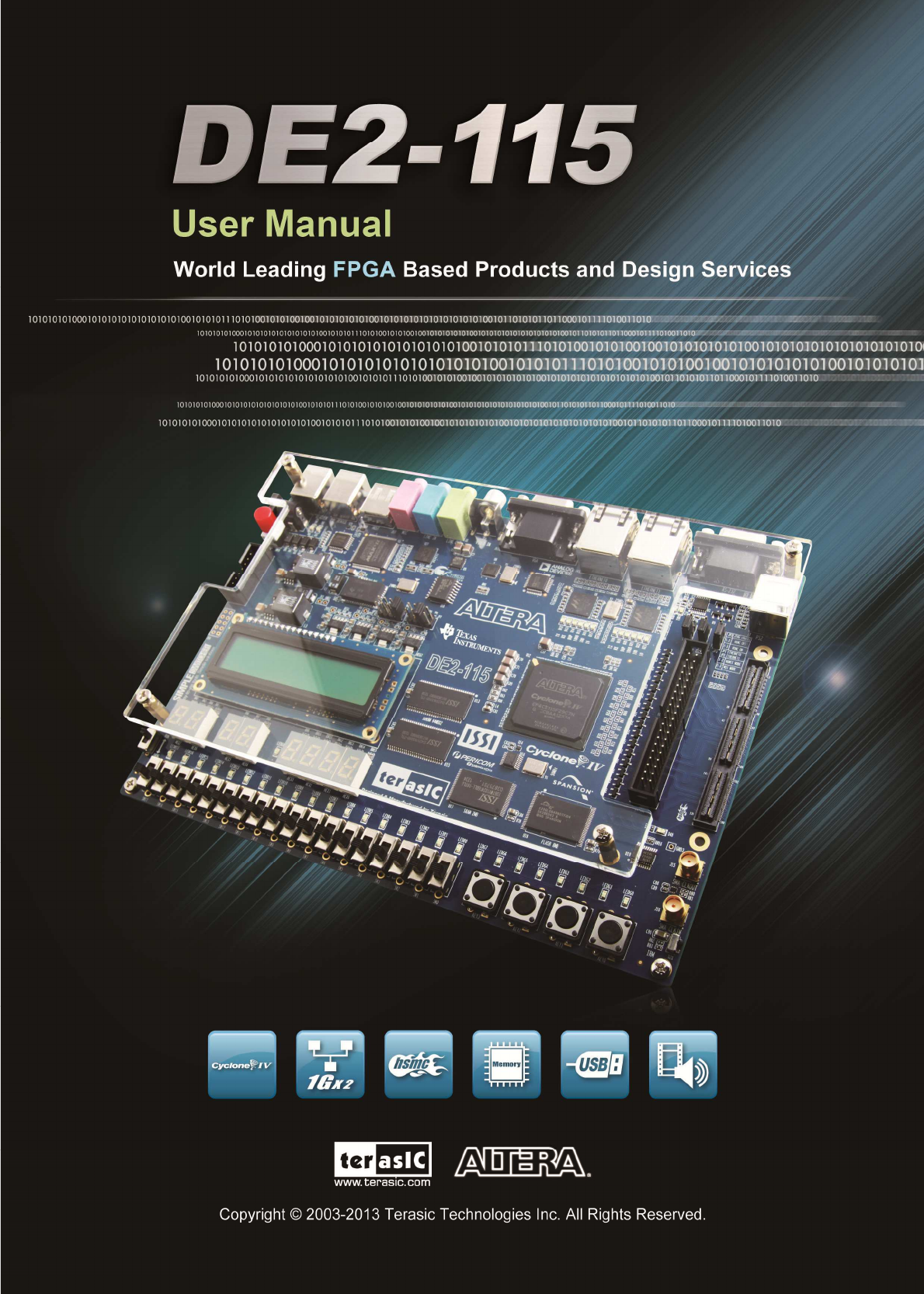

Altera DE2-115 User Manual

Browse online or download User Manual for Security device components Altera DE2-115. Altera DE2-115 User manual

- Page / 121

- Table of contents

- BOOKMARKS

- CONTENTS 2

- CONTENTSCONTENTS 2

- Chapter 1 5

- Chapter 1Chapter 1 5

- Chapter 2 8

- Chapter 2Chapter 2 8

- Terasic’s DE2-115 web pages 10

- Chapter 3 15

- Chapter 3Chapter 3 15

- Chapter 4Chapter 4 30

- Chapter 4 30

- 3.3V 1.5A 47

- “PS2_CLK” and “PS2_DAT” 56

- SRAM 64

- SDRAM 65

- FLASH 66

- EEPROM 66

- SD Card 67

- Chapter 5 72

- Chapter 5Chapter 5 72

- Input Project Name 74

- System Configuration 75

- GPIO Expansion 76

- HSMC Expansion 77

- Project Generation 79

- Chapter 6 80

- Chapter 6Chapter 6 80

- FAT File System 91

- Nios II PIO 91

- Outline 96

- Indicator Name Description 98

- Figure 6-30 SOPC Builder 113

- Chapter 7 120

- Chapter 7Chapter 7 120

Summary of Contents

1

9 • PS/2 mouse/keyboard connector • IR Receiver • 2 SMA connectors for external clock input/output • One 40-pin Expansion Header with diode p

99 Figure 6-18 Remote controller Table 6-3 Key code information for each Key on remote controller Lead Code 1bit Custom Cod

100 After the IR receiver on DE2-115 board receives this frame, it will directly transmit that to FPGA. In this demo, the IP of IR receiver cont

101 We can apply the IR receiver to many applications, such as integrating to the SD Card Demo, and you can also develop other related interestin

102 66..1100 MMuussiicc SSyynntthheessiizzeerr DDeemmoonnssttrraattiioonn This demonstration shows how to implement a Multi-tone Elec

103 Figure 6-23 Block diagram of the Music Synthesizer design Demonstration Setup, File Locations, and Instructions • Project directory:

104 Table 6-5 and Table 6-6 illustrate the usage of the slide switches, push-button switches (KEYs), PS/2 Keyboard. • Slide Switches and Push-bu

105 Figure 6-24 The Setup of the Music Synthesizer Demonstration 66..1111 AAuuddiioo RReeccoorrddiinngg aanndd PPllaayyiinngg This demon

106 Figure 6-25 Man-Machine Interface of Audio Recorder and Player Figure 6-26 shows the block diagram of the Audio Recorder and Player desig

107 Figure 6-26 Block diagram of the audio recorder and player Demonstration Setup, File Locations, and Instructions • Hardware Project d

108 Table 6-7 Slide switches usage for audio source and signal processing setting Slide Switches 0 – DOWN Position 1 – UP Position SW0 Audi

10 Figure 2-3 Block Diagram of DE2-115 Following is more detailed information about the blocks in Figure 2-3: FFPPGGAA ddeevviiccee • Cyclo

109 Figure 6-27 MII interface MAC Configuration

110 Figure 6-28 RGMII interface MAC Configuration In the MAC Options tab (See Figure 6-29), users should set up proper values for the PHY chi

111 Figure 6-29 MAC Options Configuration Once the Triple-Speed Ethernet IP configuration has been set and necessary hardware connections h

112 Figure 6-30 SOPC Builder Figure 6-31 shows the connections for programmable 10/100Mbps Ethernet operation via MII. Figure 6-31 PHY co

113 Figure 6-32 PHY connected to the MAC via RGMII After the SOPC hardware project has been built, develop the SOPC software project, whose b

114 Nios II ProcessorSoftware Device DriversHAL APIMicroC/OS-IINicheStack TCP/IP Software ComponentApplication Specific System InitializationWeb

115 Interface via JP1 and JP2 for Ethernet 0 and Ethernet 1 respectively. Table 6-9 shows the project name of web server demonstration for each E

116 • Nios II Program: web_server.elf Demo batch file folder for writing web site content zip file into flash: DE2_115_Web_Server\ WEB_SERVER_

117 Figure 6-34 System Principle Diagram Figure 6-35 Web Server Starting Success

118 Figure 6-36 Served web page for DE2-115

11 • 8MB (4Mx16) Flash with 8-bit mode • 32Kb EEPROM SSDD CCaarrdd ssoocckkeett • Provides SPI and 4-bit SD mode for SD Card access

119 Chapter 7Chapter 7Chapter 7Chapter 7 AppendixAppendixAppendixAppendix 77..11 EEPPCCSS PPrrooggrraammmmiinngg vviiaa nniiooss--2

120 77..33 CCooppyyrriigghhtt SSttaatteemmeenntt Copyright © 2012 Terasic Technologies. All rights reserved.

12 DDiissppllaayy • 16x2 LCD module SSwwiittcchheess aanndd iinnddiiccaattoorrss • 18 slide switches and 4 push-buttons switches • 18 red

13 5. Turn the RUN/PROG switch (SW19) on the left edge of the DE2-115 board to RUN position; the PROG position is used only for the AS Mode prog

14 Chapter 3Chapter 3Chapter 3Chapter 3 DE2DE2DE2DE2----115 Control Panel115 Control Panel115 Control Panel115 Control Panel The DE2-11

15 5. The DE2_115_ControlPanel.sof bit stream is loaded automatically as soon as the DE2_115_control_panel.exe is launched. 6. In

16 Figure 3-2 The DE2-115 Control Panel concept The DE2-115 Control Panel can be used to light up LEDs, change the values displ

17 Figure 3-3 Controlling LEDs Choosing the 7-SEG tab leads to the window shown in Figure 3-4. From the window, directly use the left-ri

18 Figure 3-5 Controlling the LCD display The ability to set arbitrary values into simple display devices is not needed in typ

1 CONTENTSCONTENTSCONTENTSCONTENTS CHAPTER 1 DE2-115 PACKAGE ...

19 Figure 3-6 Monitoring switches and buttons The ability to check the status of push-button and slide switch is not needed in

20 Figure 3-7 Accessing the SDRAM A 16-bit word can be written into the SDRAM by entering the address of the desired location

21 The Sequential Read function is used to read the contents of the SDRAM and fill them into a file as follows: 1. Specify the starting address

22 33..66 PPSS//22 DDeevviiccee The Control Panel provides users a PS/2 monitoring tool which monitors the real-time status of a PS/2 mouse co

23 33..77 SSDD CCaarrdd The function is designed to read the identification and specification information of the SD Card. The 4-bit SD MODE

24 2. Plug in a RS-232 9-pin male to female cable from PC to RS-232 port or a RS-232 loopback cable directly to RS-232 port. 3. The RS-232 sett

25 3. The LCD/CRT monitor will display the same color pattern on the control panel window. 4. Click the drop down menu shown in Figure

26 Figure 3-13 HSMC loopback verification test performed under Control Panel 33..1111 IIRR RReecceeiivveerr From the control panel, we can

27 Figure 3-14 Testing the IR receiver using remote controller 33..1122 OOvveerraallll SSttrruuccttuurree ooff tthhee DDEE22--111155 CC

28 Figure 3-15 The block diagram of the DE2-115 control panel

2 4.5 Clock Circuitry ...

29 Chapter 4Chapter 4Chapter 4Chapter 4 Using the DE2Using the DE2Using the DE2Using the DE2----115 Board115 Board115 Board115 Board Thi

30 JTAG chain on DE2-115 board. Shorting pin1 and pin2 on JP3 can disable the JTAG signals on HSMC connector that will form a close JTAG loop cha

31 Configuring the FPGA in JTAG Mode Figure 4-3 illustrates the JTAG configuration setup. To download a configuration bit stream into the Cyc

32 Configuring the EPCS64 in AS Mode Figure 4-5 illustrates the AS configuration setup. To download a configuration bit stream into the EPCS6

33 Figure 4-6 Connections between the push-button and Cyclone IV E FPGA Pushbutton releasedPushbutton depressedBeforeDebouncingSchmitt Trigge

34 Figure 4-8 Connections between the slide switches and Cyclone IV E FPGA 44..33 UUssiinngg LLEEDDss There are 27 user-controllable LEDs

35 Table 4-1 Pin Assignments for Slide Switches Signal Name FPGA Pin No. Description I/O Standard SW[0] PIN_AB28 Slide Switch[0] Dependi

36 LEDR[14] PIN_F15 LED Red[14] 2.5V LEDR[15] PIN_G15 LED Red[15] 2.5V LEDR[16] PIN_G16 LED Red[16] 2.5V LEDR[17] PIN_H15 LED Red[17]

37 HEX0[3] PIN_L26 Seven Segment Digit 0[3] Depending on JP7 HEX0[4] PIN_L25 Seven Segment Digit 0[4] Depending on JP7 HEX0[5] PIN_J22 Se

38 HEX6[6] PIN_AC17 Seven Segment Digit 6[6] Depending on JP6 HEX7[0] PIN_AD17 Seven Segment Digit 7[0] Depending on JP6 HEX7[1] PIN_AE17

3 6.12 Web Server Demonstration ...

39 44..66 UUssiinngg tthhee LLCCDD MMoodduullee The LCD module has built-in fonts and can be used to display text by sending

40 LCD_DATA[2] PIN_L2 LCD Data[2] 3.3V LCD_DATA[1] PIN_L1 LCD Data[1] 3.3V LCD_DATA[0] PIN_L3 LCD Data[0] 3.3V LCD_EN PIN_L4 LCD Enabl

41 Figure 4-13 HSMC VCCIO supply voltage setting header Table 4-8 Jumper Settings for different I/O Standards JP7 Jumper Settings Supplied

42 Figure 4-14 LVDS interface on HSMC connector and Cyclone IV E FPGA Table 4-9 Pin Assignments for HSMC connector Signal Name FPGA Pin No

43 HSMC_RX_D_N[0] PIN_F25 LVDS RX bit 0n or CMOS I/O Depending on JP7 HSMC_RX_D_N[1] PIN_C27 LVDS RX bit 1n or CMOS I/O Depending on JP7 HSMC_R

44 HSMC_RX_D_P[6] PIN_L23 LVDS RX bit 6 or CMOS I/O Depending on JP7 HSMC_RX_D_P[7] PIN_M25 LVDS RX bit 7 or CMOS I/O Depending on JP7 HSMC_RX_

45 HSMC_TX_D_N[12] PIN_V26 LVDS TX bit 12n or CMOS I/O Depending on JP7 HSMC_TX_D_N[13] PIN_R28 LVDS TX bit 13n or CMOS I/O Depending on JP7 HSMC

46 44..88 UUssiinngg tthhee EExxppaannssiioonn HHeeaaddeerr The DE2-115 Board provides one 40-pin expansion header. The header connects dire

47 Figure 4-16 Connections between the GPIO connector and Cyclone IV E FPGA The voltage level of the I/O pins on the expansion headers can be

48 Table 4-11 Voltage Level Setting of the Expansion Headers Using JP6 JP6 Jumper Settings Supplied Voltage to VCCIO4 IO Voltage of Expansi

4 Chapter 1Chapter 1Chapter 1Chapter 1 DE2DE2DE2DE2----115 Package115 Package115 Package115 Package The DE2-115 package contains all com

49 The factory default setting on Rs resistor will be 47 ohm and Rp resistor will not be assembled for single-ended I/O standard application. For

50 GPIO[22] PIN_AG25 GPIO Connection DATA[22] Depending on JP6 GPIO[23] PIN_AD25 GPIO Connection DATA[23] Depending on JP6 GPIO[24] PIN_AH

51 EX_IO[3] PIN_H14 Extended IO[3] 3.3V EX_IO[4] PIN_F14 Extended IO[4] 3.3V EX_IO[5] PIN_E10 Extended IO[5] 3.3V EX_IO[6] PIN_D9 Exte

52 Detailed information for using the ADV7123 video DAC is available in its datasheet, which can be found on the manufacturer’s website, or

53 SVGA(60Hz) 800x600 4 23 600 1 40 SVGA(75Hz) 800x600 3 21 600 1 49 SVGA(85Hz) 800x600 3 27 600 1 56 XGA(60Hz) 1024x768 6 2

54 (Encoder/Decoder). This chip supports microphone-in, line-in, and line-out ports, with a sample rate adjustable from 8 kHz to 96 kHz. The WM87

55 Figure 4-24 Connections between FPGA and ZT3232 (RS-232) chip Table 4-18 RS-232 Pin Assignments Signal Name FPGA Pin No. Description

56 Figure 4-26 Y-Cable use for both Keyboard and Mouse Table 4-19 PS/2 Pin Assignments Signal Name FPGA Pin No. Description I/O Standa

57 There is one jumper for each chip for switching work modes from RGMII to MII (See Figure 4-28). You will need to perform a hardware reset afte

58 Table 4-21 Jumper Settings for Working Mode of ENET0 (U8) JP1 Jumper Settings ENET0 PHY Working Mode Short Pins 1 and 2 RGMII Mode Short

5 • • Bag of six rubber (silicon) covers for the DE2-115 board stands. The bag also contains some extender pins, which can be used to facilita

59 ENET1_RX_DATA[1] PIN_C21 GMII and MII receive data[1] 2 2.5V ENET1_RX_DATA[2] PIN_A23 GMII and MII receive data[2] 2 2.5V ENET1_RX_DATA[

60 Figure 4-29 Connections between FPGA and TV Decoder Note: If the HSMC loopback adapter is mounted, the I2C_SCL will be directly routed b

61 44..1166 IImmpplleemmeennttiinngg aa TTVV EEnnccooddeerr Although the DE2-115 board does not include a TV encoder chip, the ADV7123 (10-b

62 Figure 4-31 Connections between FPGA and USB (CY7C67200) Table 4-25 USB (CY7C67200) Pin Assignments Signal Name FPGA Pin No. Descript

63 whose datasheet is offered in the DE2_115_datasheets\IR_Receiver folder on DE2-115 system CD. Note that for this all-in-one receiver module, i

64 Figure 4-33 Connections between FPGA and SRAM SDRAM The board features 128MB of SDRAM, implemented using two 64MB SDRAM devi

65 FLASH The board is assembled with 8MB of flash memory using an 8-bit data bus. The device uses 3.3V CMOS signaling standard. Because of

66 SD Card Many applications use a large external storage device, such as SD Card or CF card, for storing data. The DE2-115 board provides

67 SRAM_ADDR[15] PIN_AB11 SRAM Address[15] 3.3V SRAM_ADDR[16] PIN_AC11 SRAM Address[16] 3.3V SRAM_ADDR[17] PIN_AB9 SRAM Address[17] 3.3V

68 DRAM_DQ[3] PIN_W1 SDRAM Data[3] 3.3V DRAM_DQ[4] PIN_V3 SDRAM Data[4] 3.3V DRAM_DQ[5] PIN_V2 SDRAM Data[5] 3.3V DRAM_DQ[6] PIN_V1 SD

6 11..33 GGeettttiinngg HHeellpp Here is information of how to get help if you encounter any problem: • Terasic Technologies • Tel: +886-

69 FL_ADDR[1] PIN_AH7 FLASH Address[1] 3.3V FL_ADDR[2] PIN_Y13 FLASH Address[2] 3.3V FL_ADDR[3] PIN_Y14 FLASH Address[3] 3.3V FL_ADDR[4]

70 SD_CMD PIN_AD14 SD Command Line 3.3V SD_DAT[0] PIN_AE14 SD Data[0] 3.3V SD_DAT[1] PIN_AF13 SD Data[1] 3.3V SD_DAT[2] PIN_AB14 SD Da

71 Chapter 5Chapter 5Chapter 5Chapter 5 DE2DE2DE2DE2----115 System Builder115 System Builder115 System Builder115 System Builder This ch

72 major files which include top-level design file (.v) and Quartus II setting file (.qsf). The top-level design file contains top-level

73 Figure 5-2 The DE2-115 System Builder window Input Project Name Input project name as show in Figure 5-3. Project Name: Type in an ap

74 Figure 5-3 The DE2-115 Board Type and Project Name System Configuration Under System Configuration users are given the flexibil

75 Figure 5-4 System Configuration Group GPIO Expansion Users can connect GPIO expansion card onto GPIO header located on the DE2-115 boar

76 Figure 5-5 GPIO Expansion Group The “Prefix Name” is an optional feature which denotes the prefix pin name of the daughter card assigned i

77 Figure 5-6 HSMC Expansion Group The “Prefix Name” is an optional feature that denotes the pin name of the daughter card assigned in your d

78 Figure 5-7 Project Settings Project Generation When users press the Generate button, the DE2-115 System Builder will generate the corre

7 Chapter 2Chapter 2Chapter 2Chapter 2 Introduction of the Introduction of the Introduction of the Introduction of the Altera DE2Altera DE2

79 Chapter 6Chapter 6Chapter 6Chapter 6 Examples of Advanced DemonstrationsExamples of Advanced DemonstrationsExamples of Advanced Demonstra

80 necessary (that is, if the default factory configuration of the DE2-115 board is not currently stored in EPCS64 device), download the bit stre

81 data format. Finally, the YcrCb_to_RGB block converts the YcrCb data into RGB data output. The VGA Controller block generates sta

82 • Press KEY0 on the DE2-115 board to reset the circuit Note: If the HSMC loopback adapter is mounted, the I2C_SCL will be directly routed b

83 VGA controller to perform the real-time image storage and display. Figure 6-3 shows the block diagram of the circuit, which allows the user

84 Note: execute DE2_115_NIOS_HOST_MOUSE_VGA\demo_batch\nios_host_mouse_vga.bat will download .sof and .elf files. Figure 6-4 illustrates the

85 the status of specific components by using the USB Controller program, such as apply the “LED” Page to illumine the leds or go it out, or sele

86 o Button_Switch Control: display the status of button and switches o Hot-plug: Reconnect Figure 6-6 illustrates the setup for this demonst

87 the data input from the line-in port is then mixed with the microphone-in port and the result is sent to the line-out port. For this demonstra

88 Figure 6-8 The setup for the Karaoke Machine 66..66 SSDD CCaarrdd DDeemmoonnssttrraattiioonn Many applications use a large external st

8 Figure 2-2 The DE2-115 board (bottom view) The DE2-115 board has many features that allow users to implement a wide range of des

89 Figure 6-9 Block Diagram of the SD Card Demonstration Figure 6-10 shows the software stack of this demonstration. The Nios PIO block provi

90 MainFAT File SystemSD CardNios II PIO Figure 6-10 Software Stack of the SD Card Demonstration DDeemmoonnssttrraattiioonn SSoouurrccee CCo

91 Figure 6-11 Insert SD Card for the SD Card Demonstration Figure 6-12 Running results of the SD Card demonstration 66..77 SSDD CCaarr

92 Figure 6-13 shows the hardware block diagram of this demonstration. The system requires a 50 MHz clock provided from the board. The PLL genera

93 MainNios HALSystemCallSEG7 I2C AudioWAVE LibFAT16/FAT32SD 4-bit ModeIRReceiver Figure 6-14 Software Stack of the SD music player demonstrat

94 • • Connect a headset or speaker to the DE2-115 board and you should be able to hear the music played from the SD Card • Press KEY3 on the

95 Figure 6-15 The setup for the SD music player demonstration 66..88 PPSS//22 MMoouussee DDeemmoonnssttrraattiioonn We offer this sim

96 Data transmit from the device to controller After sending an enabling instruction to the PS/2 mouse at stream mode, the device starts to se

97 Figure 6-16 Waveforms on two lines while communication taking place Demonstration Setup, File Locations, and Instructions • Project di

98 LEDG[2] Middle button press indicator HEX0 Low byte of X displacement HEX1 High byte of X displacement HEX2 Low byte of Y displacement HEX

Comments to this Manuals